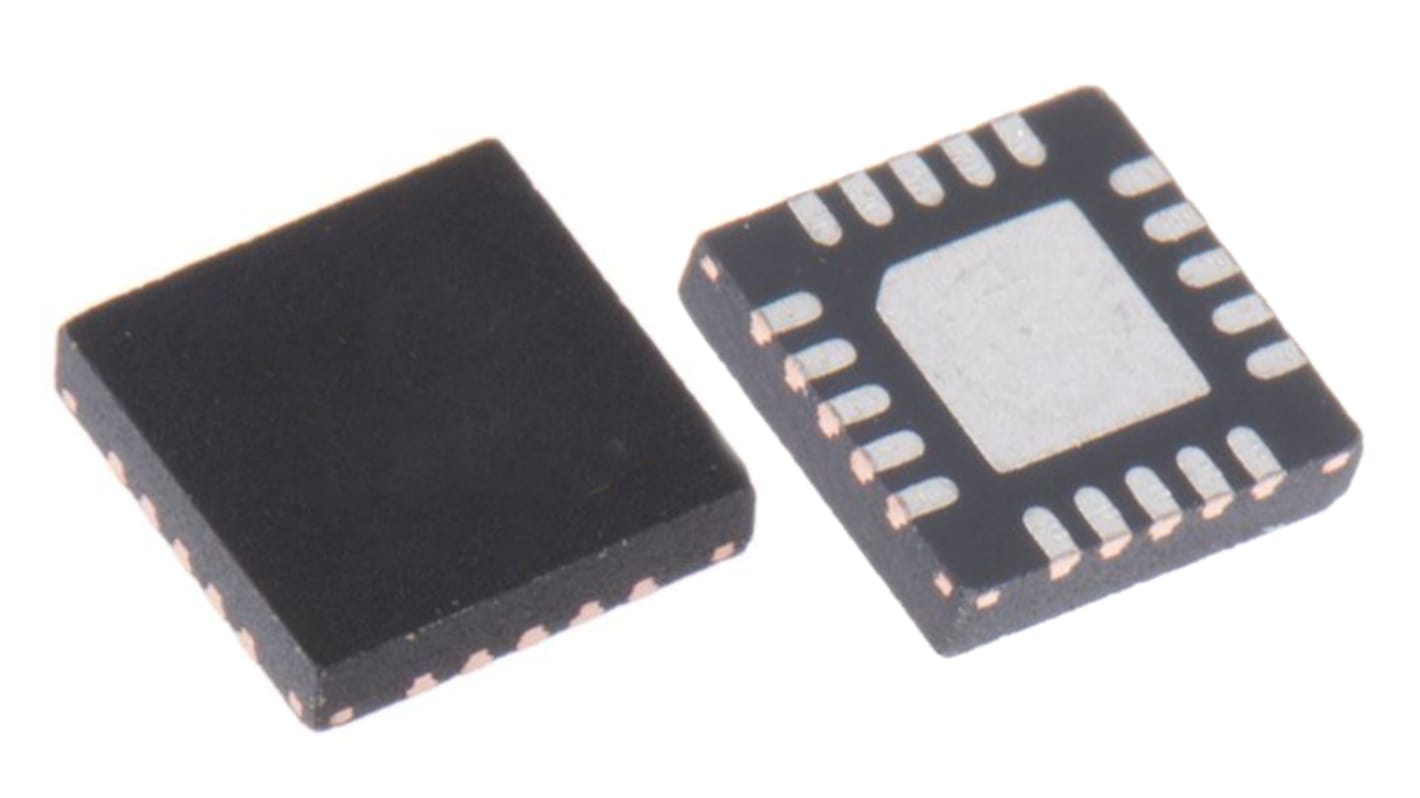

Renesas Electronics, PLL-klockgenerator 5 4.6 V, 20 Ben, VFQFPN

- RS-artikelnummer:

- 262-8958

- Tillv. art.nr:

- 5P49EE502NDGI

- Tillverkare / varumärke:

- Renesas Electronics

Mängdrabatt möjlig

Antal (1 fack med 624 enheter)*

10 483,20 kr

(exkl. moms)

13 104,00 kr

(inkl. moms)

GRATIS leverans för online beställningar över 750,00 kr

I lager

- 624 enhet(er) är redo att levereras

Behöver du mer? Ange den kvantitet du behöver och klicka på "Kontrollera leveransdatum"

Enheter | Per enhet | Per fack* |

|---|---|---|

| 624 - 624 | 16,80 kr | 10 483,20 kr |

| 1248 + | 15,884 kr | 9 911,62 kr |

*vägledande pris

- RS-artikelnummer:

- 262-8958

- Tillv. art.nr:

- 5P49EE502NDGI

- Tillverkare / varumärke:

- Renesas Electronics

Specifikationer

Datablad

Lagstiftning och ursprungsland

Produktdetaljer

Hitta liknande produkter genom att välja ett eller flera attribut.

Välj alla | Attribut | Värde |

|---|---|---|

| Varumärke | Renesas Electronics | |

| Produkttyp | PLL-klockgenerator | |

| Undertyp | Programmerbar klocka | |

| Maximal utgångsfrekvens | 120MHz | |

| Typ av fäste | Yta | |

| Kapseltyp | VFQFPN | |

| Antal ben | 20 | |

| Maximal ingångsfrekvens | 40MHz | |

| Minsta matningsspänning | -0.5V | |

| Maximal matningsspänning | 4.6V | |

| Logisk nivå för ingång | LVTTL | |

| Minsta arbetsstemperatur | -40°C | |

| Maximal arbetstemperatur | 85°C | |

| Standarder/godkännanden | RoHS | |

| Längd | 3mm | |

| Serie | 5P49EE502 | |

| Höjd | 1mm | |

| Fordonsstandard | Nej | |

| Välj alla | ||

|---|---|---|

Varumärke Renesas Electronics | ||

Produkttyp PLL-klockgenerator | ||

Undertyp Programmerbar klocka | ||

Maximal utgångsfrekvens 120MHz | ||

Typ av fäste Yta | ||

Kapseltyp VFQFPN | ||

Antal ben 20 | ||

Maximal ingångsfrekvens 40MHz | ||

Minsta matningsspänning -0.5V | ||

Maximal matningsspänning 4.6V | ||

Logisk nivå för ingång LVTTL | ||

Minsta arbetsstemperatur -40°C | ||

Maximal arbetstemperatur 85°C | ||

Standarder/godkännanden RoHS | ||

Längd 3mm | ||

Serie 5P49EE502 | ||

Höjd 1mm | ||

Fordonsstandard Nej | ||

- COO (ursprungsland):

- TH

The Renesas Electronics Versa clock low power PLL is a programmable clock generator intended for low power, battery operated consumer applications. There are four internal PLLs, each individually programmable, allowing for up to five different output frequencies. The frequencies are generated from a single reference clock. The reference clock can come from either a TCXO or fundamental mode crystal. The versa clock low power PLL can be programmed through the use of the I2C interfaces. The programming interface enables the device to be programmed when it is in normal operation or what is commonly known as in system programmable. An internal EEPROM allows the user to save and restore the configuration of the device without having to reprogram it on power-up.

2 independent adjustable VDDO groups

Programmable slew rate control

Programmable loop bandwidth settings

Programmable output inversion to reduce bimodal jitter

Individual output enable or disable

Power-down or sleep mode 10μA max in power down mode

1.8V VDD Core Voltage

Relaterade länkar

- Renesas Electronics, PLL-klockgenerator 5 4.6 V, 20 Ben, VFQFPN

- Renesas Electronics, PLL-klockgenerator 4, 32 Ben, VFQFPN

- Renesas Electronics, PLL-klockgenerator 2, 24 Ben, VFQFPN

- Renesas Electronics, PLL-klockgenerator 6, 40 Ben, VFQFPN

- Renesas Electronics, PLL-klockgenerator 3.465 V, 24 Ben, VFQFPN

- Renesas Electronics, Klockgenerator, 40 Ben, VFQFPN

- Renesas Electronics Klockgenerator, 24 Ben, VFQFPN

- Renesas Electronics Klockgenerator, 88 Ben, VFQFPN